Icarus VerilogをWindowsで使う!HDLシミュレーターの使い方

Icarus Verilogは、オープンソースのHDL(ハードウェア記述言語)シミュレーターとして、デジタル回路設計者にとって非常に有用なツールです。Windows環境でIcarus Verilogを使用することで、ユーザーは複雑なデジタルシステムのシミュレーションや検証を行えます。本記事では、Icarus Verilogのインストール方法から、基本的な使用法までを詳しく解説します。また、具体的な例を用いて、HDLコードの書き方やシミュレーションの手順を紹介します。

Windows環境でIcarus Verilogを活用する方法

本記事では、Windows環境でIcarus Verilogを使用する方法をご紹介します。Icarus Verilogは、HDL (ハードウェア記述言語) のシミュレーションと合成を行うオープンソースツールです。WindowsでHDLシミュレーターとしてIcarus Verilogを設定し、使用する手順を詳しく説明します。

Icarus Verilogのインストール方法

Icarus Verilogのインストールは簡単です。以下のステップに従ってください:

- Icarus Verilogの公式ウェブサイトから最新版のインストーラーをダウンロードします。

- ダウンロードしたインストーラーを実行します。

- インストールウィザードの指示に従い、インストールを完了させます。

- インストールが完了したら、コマンドプロンプトでivlコマンドが認識されることを確認します。

Icarus Verilogの基本的な使用方法

Icarus Verilogの基本的な使用方法は以下の通りです:

- 保存したいフォルダにVerilogソースファイル(.v 拡張子)を作成します。

- コマンドプロンプトを開き、作成したVerilogソースファイルが存在するディレクトリに移動します。

- 以下のコマンドを実行してシミュレーションを行います:

ivl -o output file source file.v

- 生成された出力ファイルを実行するためのコマンドを実行します:

vvp output file

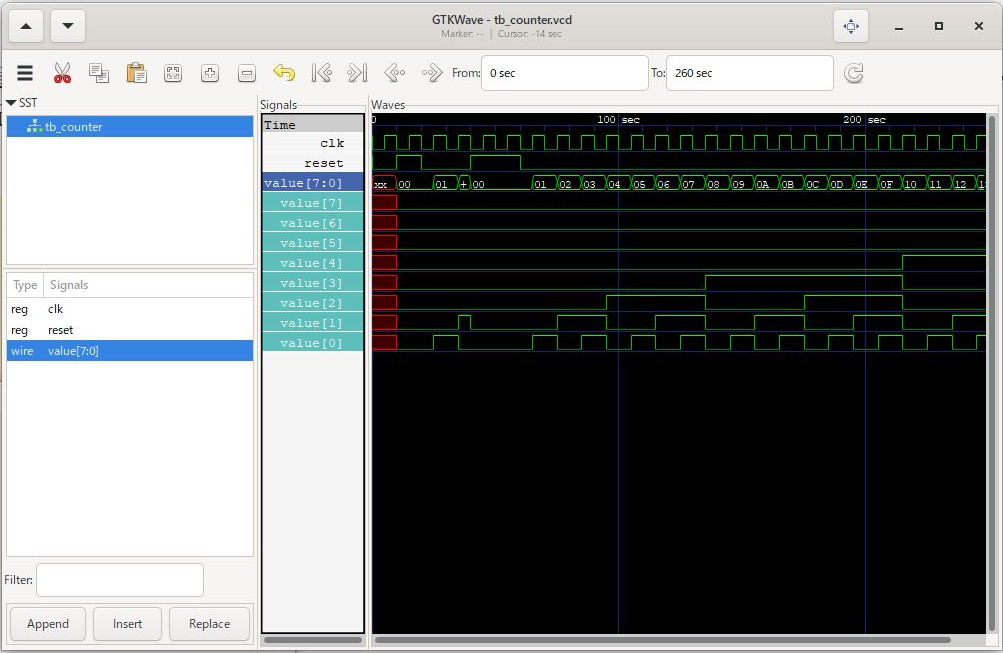

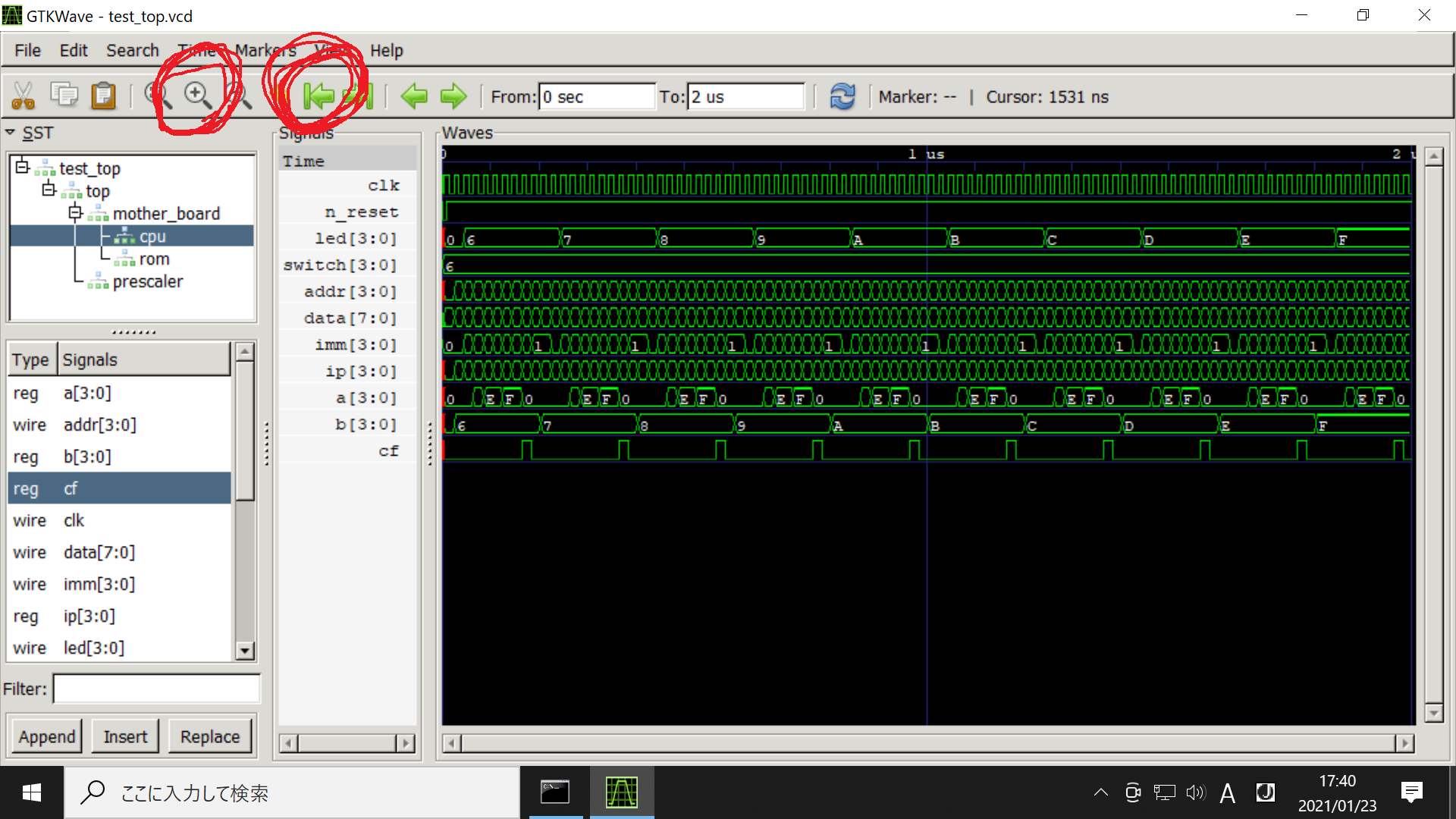

Icarus Verilogでの波形表示

Icarus Verilogでシミュレーション結果の波形表示を行うには、以下の手順に従ってください:

- gtkwaveをダウンロードしてインストールします。これは波形表示ツールです。

- シミュレーションを実行する際に、波形データをVCDファイルに出力するように指定します。以下のコマンドを使用します:

ivl -o output file -tvcd source file.v

- 生成されたVCDファイルをgtkwaveで開きます。

- gtkwaveで波形を表示し、シミュレーション結果を確認します。

Icarus Verilogのエラーメッセージの理解

Icarus Verilogを使用する際には、様々なエラーメッセージが表示されることがあります。エラーメッセージを理解し、適切に対処することで効率的な開発ができます。

- エラーメッセージは通常、以下のような形式で表示されます:

source file.v:行番号: エラー詳細

- エラーメッセージの行番号とエラー詳細に基づいて、問題のある部分を特定します。

- 一般的なエラーメッセージとその対処方法は以下の通りです:

エラーメッセージ 対処方法 Module 名前 not found 指定したモジュールが存在しないか、ファイルに含まれていないことを確認します。 Port 名前 is not declared ポートが正しく宣言されていないことを確認します。 Syntax error at or near トークン 文法エラーを修正します。通常、括弧やセミコロンの位置が間違っている可能性があります。 Cannot find the ファイル 指定したファイルのパスが正しいことを確認します。

Icarus Verilogの高度な機能

Icarus Verilogは高度な機能も提供しており、以下のように使用することができます:

- コンパイルオプションを指定して最適化を行います。例えば、以下のコマンドで最適化レベルを指定できます:

ivl -O2 -o output file source file.v

- パラメータを使用してモジュールの挙動を動的に変更します。例えば、以下のコードでパラメータを定義できます:

module example (parameter WIDTH = 8) (input [WIDTH-1:0] in, output reg [WIDTH-1:0] out); always @() out = in; endmodule

- タスクと関数を使用してコードの再利用性を高めます。例えば、以下のコードでタスクを定義できます:

module example; task display; input [7:0] value; $display(Value: %d, value); endtask initial begin display(42); end endmodule

Icarus Verilogとは何ですか?

Icarus Verilogとは、オープンソースのハードウェア記述言語(HDL)であるVerilogのためのコンパイラです。Icarus Verilogは、Verilogコードを中間形式に変換し、その中間形式をさまざまな対象に変換することができます。主な用途は、シミュレーション、テストベンチの実行、およびFPGAやASICの合成にあります。Icarus Verilogは、IEEE Std 1364-2005までの標準をサポートしています。

Icarus Verilogの特徴

Icarus Verilogは、多様な特徴を持ち、広範な用途に利用されています。以下に主な特徴をまとめます。

- オープンソース:Icarus Verilogは、GNU General Public License (GPL)の下で公開されており、ユーザーは無料で使用できます。

- 多様なプラットフォーム対応:Linux、Windows、macOSなど、さまざまなオペレーティングシステム上で動作します。

- 柔軟な拡張性:プラグインや外部ツールとの連携が可能で、ユーザーが独自の機能を追加することができます。

Icarus Verilogのインストール方法

Icarus Verilogのインストールは比較的簡単で、以下の手順に従うことで完了します。

- ソースコードからビルド:公式リポジトリからソースコードを取得し、必要に応じてコンパイルします。

- パッケージマネージャーを使用:主要なオペレーティングシステムにはパッケージマネージャーが用意されており、それらを利用してインストールできます。

- バイナリファイルのダウンロード:公式ウェブサイトからバイナリファイルをダウンロードし、インストール手順に従います。

Icarus Verilogの使用例

Icarus Verilogを使用する際の具体的な例を以下に示します。

- シンプルなVerilogコードのシミュレーション:基本的な論理回路を定義し、`iverilog`コマンドでコンパイルし、`vvp`コマンドでシミュレーションを実行します。

- FPGAへの合成:Icarus Verilogで生成された中間形式をFPGA合成ツールに渡し、目標デバイスに展開します。

- テストベンチの使用:複雑なロジックをテストするために、テストベンチを記述し、その機能を検証します。

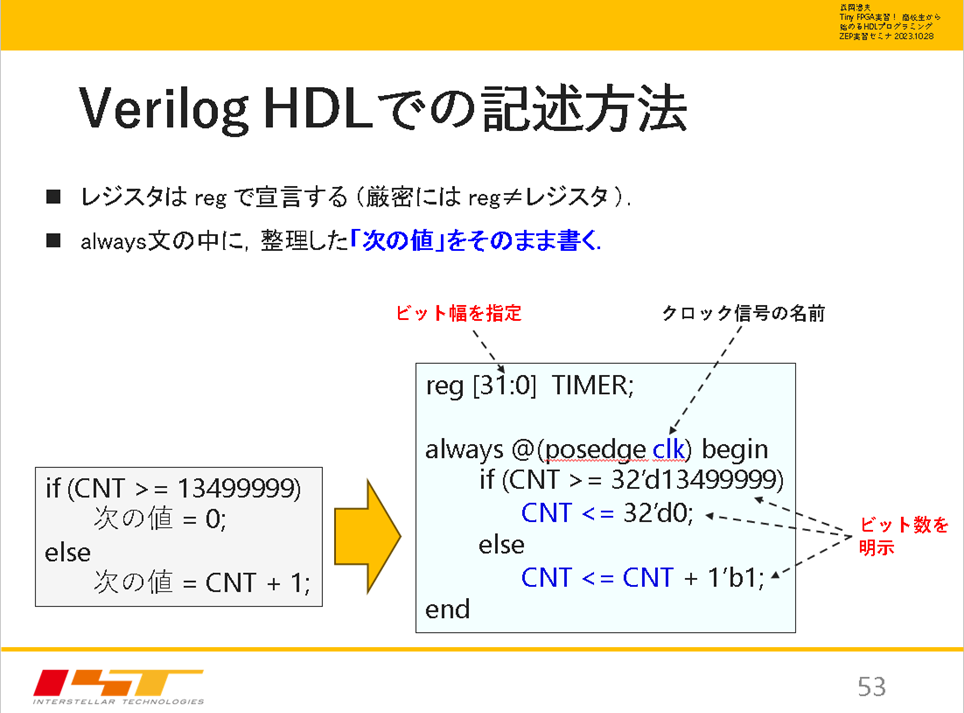

Verilog HDLとは何ですか?

Verilog HDLとは、ハードウェア記述言語(Hardware Description Language: HDL)の一種で、主にデジタル回路の設計と検証に使用されます。Verilog HDLは1980年代に開発され、1995年にIEEE標準(IEEE 1364)として認定されました。この言語は、組み込みシステム、ASIC(Application-Specific Integrated Circuit)、FPGA(Field-Programmable Gate Array)などの設計に広く利用されています。

Verilog HDLの特徴

Verilog HDLの主な特徴は、その柔軟性と表現力にあります。詳細には以下の通りです:

- 階層的な記述:Verilog HDLでは、複雑な設計を小さなブロックに分割し、それらを階層的に結合することができます。これにより、設計の管理と再利用が容易になります。

- 抽象度の調整:Verilog HDLでは、回路の抽象度を制御することができます。 Behavioral、RTL(Register-Transfer Level)、Gate Levelなどの異なる抽象度で設計を記述できます。

- シミュレーション機能:Verilog HDLには強力なシミュレーション機能が組み込まれており、設計の動作を事前に検証することができます。

Verilog HDLの文法

Verilog HDLの文法は、C言語に似ており、その基本構文は以下のような特徴を持っています:

- モジュールとインスタンス:Verilog HDLでは、モジュールという単位で設計を定義します。モジュール内では、入力と出力のポート、内部の信号、およびロジックを記述します。モジュールは他のモジュール内でインスタンス化できます。

- 戦略的な記述:Verilog HDLでは、プロセス(alwaysブロック)、コンティニュアス(assign文)などの記述方法があり、これらの戦略的な記述を使用して、組み込みシステムの動作を詳細に制御できます。

- データ型と演算子:Verilog HDLでは、bit型、integer型、real型などのデータ型と、ビット操作や論理演算などの演算子を使用できます。

Verilog HDLの用途

Verilog HDLは、さまざまな用途に使用され、その主要な用途は以下の通りです:

- ASIC設計:Verilog HDLは、カスタムチップの設計に広く使用されています。ASIC設計では、高性能と低消費電力を達成するために、Verilog HDLで設計を記述し、Synthesisツールを使って回路を最適化します。

- FPGA開発:FPGA(Field-Programmable Gate Array)の開発では、Verilog HDLを使用して回路を設計し、FPGAデバイスにプログラムします。FPGAは、設計の変更が容易であるため、プロトタイピングや高速化に適しています。

- テストベンチの作成:Verilog HDLは、設計の検証用のテストベンチの作成にも使用されます。テストベンチでは、設計の入力信号を生成し、出力信号を確認することで、設計の正しさを検証します。

Verilogは何に使われる言語ですか?

Verilogはハードウェア記述言語(Hardware Description Language, HDL)の一種で、主にデジタル論理回路のデザインとシミュレーションに使われます。この言語はVLSI(Very Large Scale Integration)チップの設計、テストベンチの作成、システムの機能検証など、様々な用途に使用されます。Verilogは1980年代に開発され、IEEE 1364規格として標準化され、現在でも広く利用されています。

Verilogの主な用途

Verilogは主に以下のような用途に使用されます:

- デジタル回路の設計:Verilogを用いてデジタル回路を記述することで、論理ゲートやレジスタ、メモリなどの基本的な構成要素を簡単に定義できます。

- シミュレーション:設計した回路をシミュレーションすることにより、その動作を確認し、バグやエラーを検出することが可能です。

- テストベンチの作成:テストベンチは、設計した回路の動作を検証するために使用されます。Verilogを用いてテストベンチを作成することで、入力信号を生成し、出力信号を検証できます。

Verilogの特徴

Verilogは以下の特徴を持っています:

- 高い抽象度:Verilogは回路を不同な抽象度で記述できるため、簡単に複雑なシステムを設計できます。

- 並列処理の表現:Verilogは並列処理を自然に表現できるため、ハードウェアの並列性を活用した設計が可能です。

- シミュレーションサポート:Verilogは豊富なシミュレーション機能を提供しており、設計の検証を効率的に行うことができます。

Verilogと他のHDLとの比較

Verilogは他のHDL言語と比べて以下の特徴があります:

- 構文の簡潔さ:Verilogの構文はC言語に似ているため、プログラミングの知識がある人にとって学習が比較的容易です。

- スケーラビリティ:Verilogは小さな回路から大規模なシステムまで幅広いスケールの設計に適しています。

- コミュニティとサポート:Verilogには活発なコミュニティがあり、多くの開発ツールやリソースが利用できます。

よくある疑問

Icarus VerilogをWindowsでインストールする方法は?

Icarus VerilogをWindowsでインストールするには、まずIcarus Verilogの公式ウェブサイトや信頼できるソースから最新のインストーラーをダウンロードします。ダウンロードが完了したら、インストーラーを実行し、指示に従ってインストールプロセスを進めてください。インストール中にインストールパスや追加の設定を確認し、必要に応じてカスタマイズすることもできます。インストールが完了したら、コマンドプロンプトやターミナルからivlコマンドを使用して、Icarus Verilogが正しくインストールされていることを確認できます。

Icarus VerilogでHDLシミュレーションを行う基本手順は?

Icarus Verilogを使用してHDLシミュレーションを行うには、まずVerilogソースコードファイルを作成します。次に、コマンドプロンプトやターミナルでivlコマンドを使用して、ソースコードをコンパイルします。コンパイルが成功したら、vvpコマンドを使用してシミュレーションを実行します。シミュレーションの結果は、指定した出力ファイルや標準出力に表示されます。また、シミュレーション中にテストベンチを使用して、モジュールの動作を詳細に検証することも可能です。

Icarus Verilogを使って複雑な設計をシミュレートする方法は?

複雑な設計をIcarus Verilogでシミュレートするには、まずモジュールの分割と階層化を適切に行います。各モジュールを個別にテストし、機能を確認します。次に、各モジュールをテストベンチに統合し、システム全体の動作を検証します。シミュレーション中に問題が発生した場合は、波形ビューアを使用して信号を可視化し、問題の原因を特定します。また、アサートやカバレッジ機能を活用して、設計の完全性を確保することもできます。

Icarus Verilogでエラーをデバッグする際の一般的な手法は?

Icarus Verilogでエラーをデバッグする際には、まずコンパイルエラーやシミュレーションエラーのメッセージを詳細に確認します。エラーメッセージが指示する行数やファイルを参照し、ソースコードを修正します。また、波形ビューアを使用して、シミュレーション中に発生する信号の変化を可視化し、問題の原因を特定します。さらに、プリプロセッサディレクティブやデバッグ用の出力ステートメントをソースコードに追加して、内部状態を確認することも有効です。これらの方法を組み合わせることで、効率的にエラーを特定し、設計を改善できます。

コメントを残す